Hot Posts

Western Digital Previews 4 TB SD Card: World's Highest-Capacity Western Digital this week is previewing the industry's first 4 TB SD card. The device is being showcased at the NAB trade show for broadcasters and content creators and will be released commercially in 2025.

Western Digital's SanDisk Extreme Pro SDUC 4 TB SD card complies with the Secure Digital Ultra Capacity standard (SDUC, which enables up to 128TB). The card uses the Ultra High Speed-I (UHS-I) interface and is rated for speed Class 10, therefore supporting a minimum speed of 10 MB/s and a maximum data transfer rate of 104 MB/s when working in UHS104 (SDR104) mode (there is a catch about performance, but more on that later). WD's SD card is also rated to meet Video Speed Class V30, supporting a minimal sequential write speed of 30 MB/s, which is believed to be good enough for 8K video recording, above and beyond the 4K video market that Western Digital is primarily aiming the forthcoming card at.

For now, Western Digital is not disclosing what NAND is in the SanDisk Extreme Pro SDUC 4 TB SD card. Given the high capacity and relatively distant 2025 release date, WD may be targetting this as one of their first products to use their forthcoming BiCS 9 NAND.

And while not listed in WD's official press release, we would be surprised if the forthcoming card didn't also support the off-spec DDR200/DDR208 mode, which allows for higher transfer rates than the UHS-I standard normally allows via double data rate signaling. Western Digital's current-generation SanDisk Extreme Pro SDXC 1 TB SD card already supports that mode, allowing it to reach read speeds as high as 170 MB/s, so it would be surprising to see the company drop it from newer products. That said, the catch with DDR208 remains the same as always: it's a proprietary mode that requires a compatible host to make use of.

Western Digital has not disclosed how much will its SanDisk Extreme Pro SDUC 4 TB SD card cost. A 1 TB SanDisk Extreme Pro card costs $140, so one can make guesses about the price of a 4 TB SD card that uses cutting-edge NAND.

Storage

The Eurocom 780W AC Power Adapter Review: Big Power For Big Laptops While desktop PC power supplies receive the bulk of enthusiasts’ attention for good reasons – not the least of which being the vast selection of options that comes from being a standardized part – power supplies as a whole aren’t just a concern for big PCs. With the majority of PC sales having flipped to notebook sales some years ago, notebook power supplies already lead the market in volume. And while most laptops don’t need the kind of massively powered PSUs that dominate the desktop space, even that is slowly changing as desktop replacement-class laptops increasingly grow in performance and power consumption.

Perhaps the poster-child for the high-performance, high-powered laptop is Eurocom, who has a long history of developing heavy-duty DTR laptops that are all but portable desktop systems. Following recent trends in GPU power consumption and in GPU popularity for both gaming and AI workloads, the company has been selling a range of “mobile supercomputers”, which are practically large, tailor-made laptops that rival even the best of desktop computers – and have the power requirements to match.

In order to power their own high-end laptops, Eurocom has developed a rather unusual 780W AC adapter for high-performance laptops. Intended to power the most powerful of powerful laptops, their latest power adapter can supply over three-quarters of a kilowatt of DC power; a desktop-like wattage for a desktop-like device. It’s a laptop power adapter that’s unique in its scale, and with some room to scale up even further.

| Eurocom 780W AC Adapter Power specifications |

|

| RAIL | +20V |

| MAX OUTPUT | 39A |

| 780W | |

| DIMENSIONS | 325 x 110 x 40mm, 1.38kg |

| AC INPUT | 90 - 264 VAC, 50 - 60 Hz |

| MSRP | PSU: $299, Cable: $129+ |

Eurocom has offered this adapter for a few years now. But it’s taken on a new life as more laptops have been released that use such a large adapter (or two smaller 300W-ish power adapters). And, critically, Eurocom has made additional DC cable/connector sets for other manufactuers’ laptops, significantly increasing the number of systems it’s compatible with. Currently, Eurocom offers DC cables for the following laptops:

- Alienware M17x M18x; 1x DC Cable ; w/ barrel AW connector; 193cm/6.4ft

- Alienware AREA 51m; 1x DC Cable + Splitter Box w/ 2x barrel AW connectors; 152cm/5ft

- ASUS ROG G18 Strix; GX501V; GM501; GM501GM; GX531GM; 1x DC Cable; w/ barrel ROG connector

- ASUS G703GX, GZ700GX; 1x DC Cable w/ 2x ROG barrel connectors; 152cm/5ft

- CLEVO, OriginPC, Sager, XMG, EUROCOM laptops; 1x DC Cable; w/ 4-pin round connector; 182cm / 6ft

- CLEVO X370SNx; 1x DC Cable; w/ square connector; 120cm / 3.8ft

- CLEVO X170SM/X170KM; 1x DC Cable; w/ dual square connectors; 152cm / 5ft

- Dell Precision 7720/7710; 1x DC Cable; w/ barrel Dell connector; 120cm / 3.8ft

- MSI GE76, GT76, GT77, GE78HX Raider, Titan 18HX 1x DC Cable; w/ single square connector; 120cm / 3.8ft

- MSI laptops & MSI Trident AS Gaming Desktops; 1x DC Cable; w/ 4-pin round connector; 182cm / 6ft

The Eurocom 780W AC Adapter

Externally, the Eurocom 780W AC adapter looks like a hybrid between a PC PSU and a laptop adapter. It is shaped like an oversized laptop AC adapter but has a metallic body and cooling vents/fans. Eurocom advertises that it weighs “only 1.34kg”, which is the weight of an entire 14-inch laptop by comparison, but is relatively lightweight for a PSU with that kind of power output. The company logo is debossed across the top side of the adapter, with four round anti-slip pads found at its bottom. Care needs to be taken while moving it around because the metallic edges and weight can spell trouble for wooden surfaces.

Eurocom installed a small information display on the AC adapter, which shows the current, voltage, and power output, as well as the temperature of the adapter. It is not perfectly accur... Cases/Cooling/PSUs

In Light of Stability Concerns, Intel Issues Request to Motherboards Vendors to Actually Follow Stock Power Settings Across the internet, from online forums such as Reddit to various other tech media outlets, there's a lot of furor around reports of Intel's top-end 14th and 13th Gen K series of processors running into stability issues. As Intel's flagship chips, these parts come aggressively clocked in order to maximize performance through various implementations of boost and turbo, leaving them running close to their limits out of the box. But with high-end motherboards further goosing these chips to wring even more performance out of them, it would seem that the Intel desktop ecosystem has finally reached a tipping point where all of these efforts to boost performance have pushed these flagship chips to unstable conditions. To that end, Intel has released new gudiance to its consumer motherboard partners, strongly encouraging them to actually implment Intel's stock power settings, and to use those baseline settings as their out-of-the-box default.

While the underlying conditions are nothing new – we've published stories time and time again about motherboard features such as multi-core enhancement (MCE) and raised power consumption limits that seek to maximize how hard and how long systems are able to turbo boost – the issue has finally come to a head in the last couple of months thanks to accumulating reports of system instability with Intel's 13900K and 14900K processors. These instability problems are eventually solved by either tamping down on these motherboard performance-boosting features – bringing the chips back down to something closer to Intel's official operating parameters – or downclocking the chips entirely.

Intel first began publicly investigating the matter on the 27th of February, when Intel's Communications Manager, Thomas Hannaford, posted a thread on Intel's Community Product Support Forms titled "Regarding Reports of 13th/14th Gen Unlocked Desktop Users Experiencing Stability Issues". In this thread, Thomas Hannaford said, "Intel is aware of reports regarding Intel Core 13th and 14th Gen unlocked desktop processors experiencing issues with certain workloads. We're engaged with our partners and are conducting analysis of the reported issues. If you are experiencing these issues, please reach out to Intel Customer Support for further assistance in the interim."

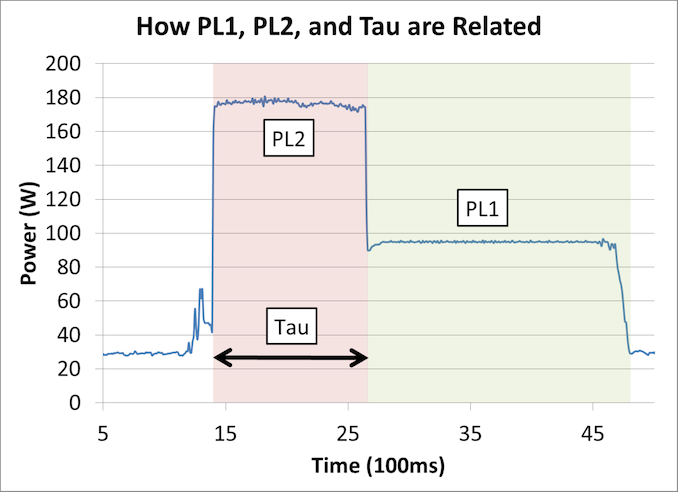

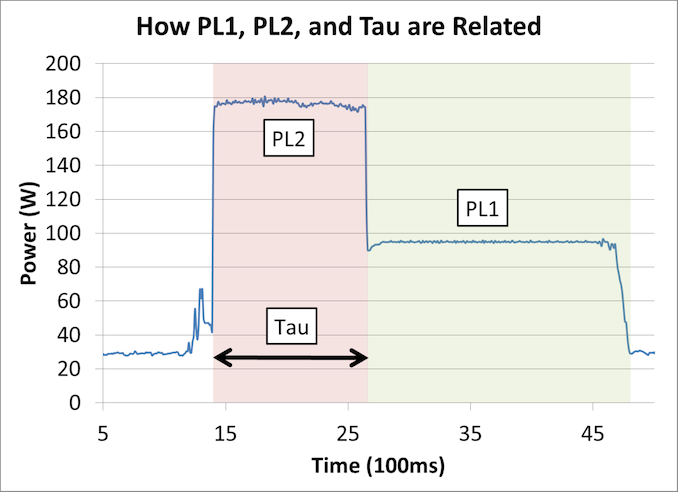

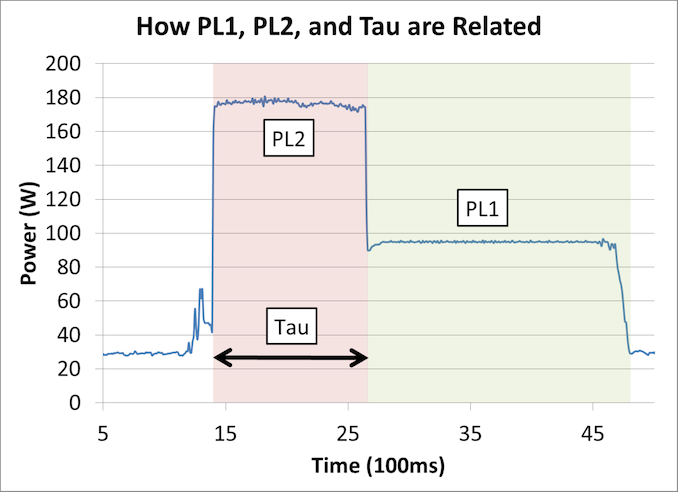

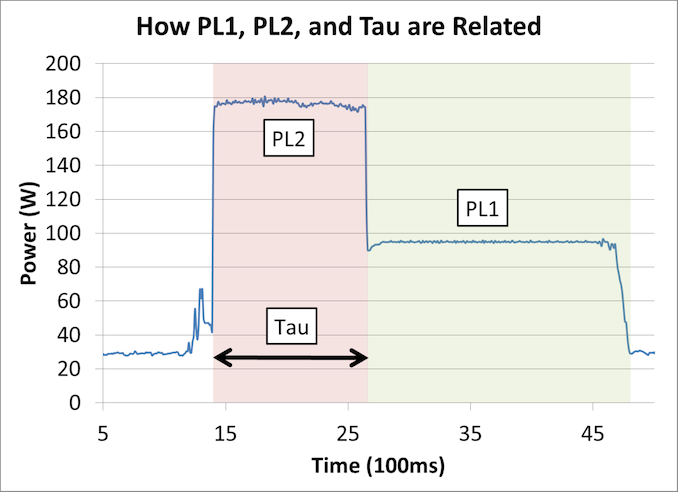

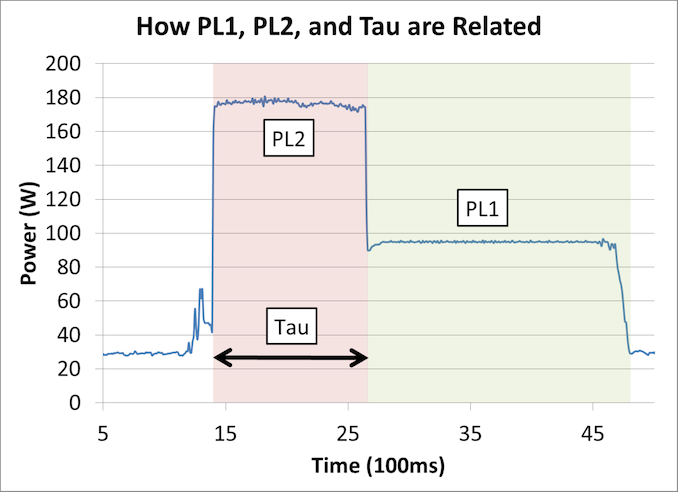

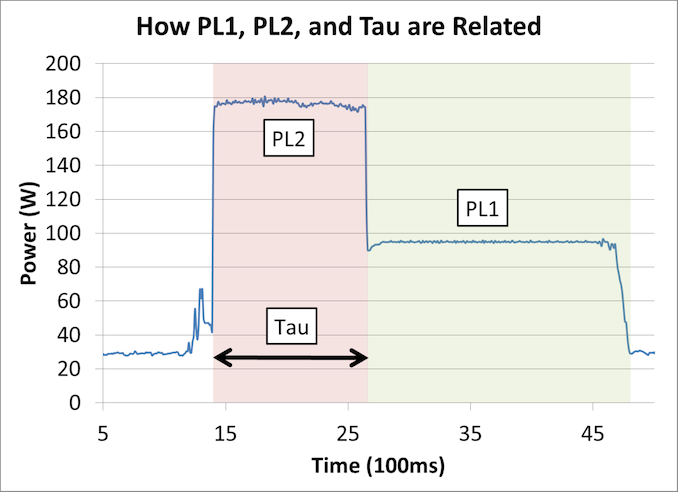

Since that post went up, additional reports have been circulating about instability issues across various online forums and message boards. The underlying culprit has been theorized to be motherboards implementing an array of strategies to improve chip performance, including aggressive multi-core enhancement settings, "unlimited" PL2 turbo, and reduced load line calibration settings. At no point do any of these settings overclock a CPU and push it to a higher clockspeed than it's validated for, but these settings do everything possible to keep a chip at the highest clockspeed possible at all times – and in the process seem to have gone a step too far.

From "Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained"

We wrote a piece initially covering multi-core enhancement in 2012, detailing how motherboard manufacturers try to stay competitive with each other and leverage any headroom within the silicon to output the highest performance levels. And more recently, we've talked about how desktop systems with Intel chips are now regularly exceeding their rated TDPs – sometimes by extreme amounts – as motherboard vendors continue to push them to run as hard as possible for the best performance.

But things have changed since 2012. At the time, this wasn't so much of an issue, as overclocking was actually very favorable to increasing the performance of processors. But in 2024 with chips such as the Intel Core i9-14900K, we have CPUs shipping with a maximum turbo clock speed of 6.0 GHz and a peak power consumption of over 400 Watts, figures that were only a pipe dream a decade ago.

Jumping to the present time, over the weekend Intel released a statement about the matter to its partners, outlining their investigation so far and their sug... CPUs

From "Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained"

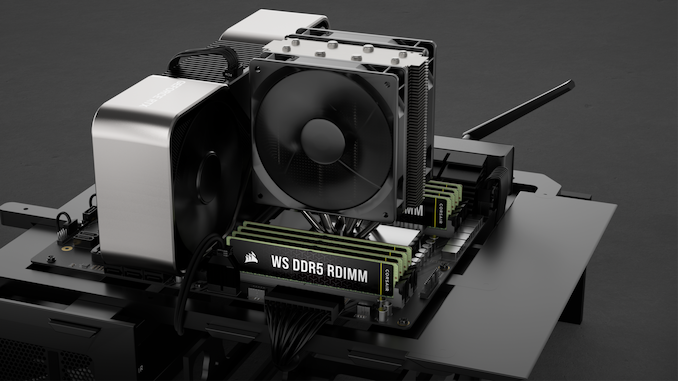

Corsair Enters Workstation Memory Market with WS Series XMP/EXPO DDR5 RDIMMs Corsair has introduced a family of registered memory modules with ECC that are designed for AMD's Ryzen Threadripper 7000 and Intel's Xeon W-2400/3400-series processors. The new Corsair WS DDR5 RDIMMs with AMD EXPO and Intel XMP 3.0 profiles will be available in kits of up to 256 GB capacity and at speeds of up to 6400 MT/s.

Corsair's family of WS DDR5 RDIMMs includes 16 GB modules operating at up to 6400 MT/s with CL32 latency as well as 32 GB modules functioning at 5600 MT/s with CL40 latency. At present, Corsair offers a quad-channel 64 GB kit (4×16GB, up to 6400 MT/s), a quad-channel 128GB kit (4×32GB, 5600 MT/s), an eight-channel 128 GB kit (8×16GB, 5600 MT/s), and an eight-channel 256 GB kit (8×32GB, 5600 MT/s) and it remains to be seen whether the company will expand the lineup.

Corsair's WS DDR5 RDIMMs are designed for AMD's TRX50 and WRX90 platforms as well as Intel's W790 platform and are therefore compatible with AMD's Ryzen Threadripper Pro 7000 and 7000WX-series as well as Intel's Xeon W-2400/3400-series CPUs. The modules feature both AMD EXPO and Intel XMP 3.0 profiles to easily set their beyond-JEDEC-spec settings and come with thin heat spreaders made of pyrolytic graphite sheet (PGS), which thermal conductivity than that of copper and aluminum of the same thickness. For now, Corsair does not disclose which RCD and memory chips its registered memory modules use.

Unlike many of its rivals among leading DIMM manufacturers, Corsair did not introduce its enthusiast-grade RDIMMs when AMD and Intel released their Ryzen Threadripper and Xeon W-series platforms for extreme workstations last year. It is hard to tell what the reason for that is, but perhaps the company wanted to gain experience working with modules featuring registered clock drivers (RCDs) as well as AMD's and Intel's platforms for extreme workstations.

The result of the delay looks to be quite rewarding: unlike modules from its competitors that either feature AMD EXPO or Intel XMP 3.0 profiles, Corsair's WS DDR5 RDIMMs come with both. While this may not be important on the DIY market where people know exactly what they are buying for their platform, this is a great feature for system integrators, which can use Corsair WS DDR5 RDIMMs both for their AMD Ryzen Threadripper and Intel Xeon W-series builds, something that greatly simplifies their inventory management.

Since Corsair's WS DDR5 RDIMMs are aimed at workstations and are tested to offer reliable performance beyond JEDEC specifications, they are quite expensive. The cheapest 64 GB DDR5-5600 CL40 kit costs $450, the fastest 64 GB DDR5-6400 CL32 kit is priced at $460, whereas the highest end 256 GB DDR5-5600 CL40 kit is priced at $1,290.

Memory

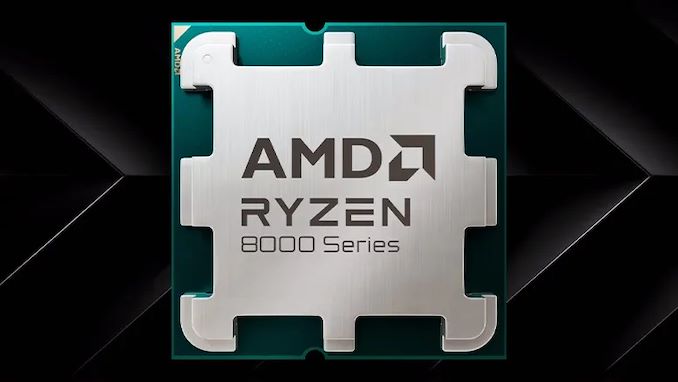

AMD Quietly Launches Ryzen 7 8700F and Ryzen 5 8400F Processors AMD has recently expanded its Ryzen 8000 series by introducing the Ryzen 7 8700F and Ryzen 5 8400F processors. Initially launched in China, these chips were added to AMD's global website, signaling they are available worldwide, apparently from April 1st. Built from the recent Zen 4-based Phoenix APUs using the TSMC 4nm node as their Zen 4 mobile chips, these new CPUs lack integrated graphics. However, the Ryzen 7 8700F does include the integrated Ryzen AI NPU for added capabilities in a world currently dominated by AI and moving it directly into the PC.

The company's decision to announce these chips in China aligns with its strategy to offer Ryzen solutions at every price point in the market. Although AMD didn't initially disclose the full specifications of these F-series models, and we did reach out to the company to ask about them, they refused to discuss them with us. Their listing on the website has now been updated with a complete list of specifications and features, with everything but the price mentioned.

| AMD Ryzen 8000G vs. Ryzen 8000F Series (Desktop) Zen 4 (Phoenix) |

|||||||||

| AnandTech | Cores/Threads | Base Freq |

Turbo Freq |

GPU | GPU Freq |

Ryzen AI (NPU) |

L3 Cache (MB) |

TDP | MSRP |

| Ryzen 7 | |||||||||

| Ryzen 7 8700G | 8/16 | 4200 | 5100 | R780M 12 CUs |

2900 | Y | 16 | 65W | $329 |

| Ryzen 7 8700F | 8/16 | 4100 | 5000 | - | - | Y | 16 | 65W | ? |

| Ryzen 5 | |||||||||

| Ryzen 5 8600G | 6/12 | 4300 | 5000 | R760M 8 CUs |

2800 | Y | 16 | 65W | $229 |

| Ryzen 5 8400F | 6/12 | 4200 | 4700 | - | - | N | 16 | 65W | ? |

The Ryzen 7 8700F features an 8C/16T design, with 16MB of L3 cache and the same 65W TDP as the Ryzen 7 8700G. Although the base clock speed is 4.1 GHz, it boosts to 5.0 GHz; this is 100 MHz less on both base/boost clocks than the 8700G. Meanwhile, the Ryzen 5 8400F is a slightly scaled-down version of the Ryzen 8600G APU, with 6C/12, 16MB of L3 cache, and again has a 100 MHz reduction to base clocks compared to the 8600G. Unlike the Ryzen 5 8400F, the Ryzen 7 8700F keeps AMD's Ryzen AI NPU, adding additional capability for generative AI.

The Ryzen 5 8400F can boost up to 4.7 GHz, 300 MHz slower than the Ryzen 5 8600G. AMD also allows overclocking for these new F-series chips, which means users could potentially boost the performance of these processors to match their G-series equivalents.

Pricing details are still pending, but to remain competitive, AMD will likely need to price these CPUs below the 8700G and 8600G, as well as the Ryzen 7 7700 and Ryzen 5 7600. These CPUs offer, albeit very limited, integrated graphics and have double the L3 cache capacity, along with higher boost clocks than the 8000F series chips, so pricing is something to consider whenever pricing becomes available.

CPUs

Seagate: Mozaic 3+ HAMR Hard Drives Can Last Over Seven Years As Seagate ramps up shipments of its new heat assisted magnetic recording (HAMR)-based Mozaic 3+ hard drive platform, the company is both in the enviable position of shipping the first major new hard drive technology in a decade, and the much less enviable position of proving the reliability of the first major new hard drive technology in a decade. Due to HAMR's use of temporal heating with its platters, as well as all-new read/write heads, HAMR introduces multiple new changes at once that have raise questions about how reliable the technology will be. Looking to address these matters (and further promote their HAMR drives), Seagate has published a fresh blog post outlining the company's R&D efforts, and why the company expects their HAMR drives to last several years – as long or longer than current PMR hard drives.

According to the company, the reliability of Mozaic 3+ drives on par with traditional drives relying on perpendicular magnetic recording (PMR), the company says. In fact, components of HAMR HDDs have demonstrated a 50% increase in reliability over the past two years. Seagate says that Mozaic 3+ drives boast impressive durability metrics: their read/write heads have demonstrated capacity to handle over 3.2 petabytes of data transfer over 6,000 hours of operation, which exceeds data transfers of typical nearline hard drives by 20 times. Accordingly, Seagate is rating these drives for a mean time between failure (MTBF) 2.5 million hours, which is in-line with PMR-based drives.

Based on their field stress tests, involving over 500,000 Mozaic 3+ drives, Seagate says that the heads of Mozaic 3+ drives will last over seven years, surpassing the typical lifespan of current PMR-based drives. Generally, customers anticipate that modern PMR drives will last between four and five years with average usage, so these drives would exceed current expectations.

Altogether, Seagate is continuing aim for a seamless transition from PMR to HAMR drives in customer systems. That means ensuring that these new drives can fit into existing data center infrastructures without requiring any changes to enterprise specifications, warranty conditions, or form factors.

Storage

In Light of Stability Concerns, Intel Issues Request to Motherboards Vendors to Actually Follow Stock Power Settings Across the internet, from online forums such as Reddit to various other tech media outlets, there's a lot of furor around reports of Intel's top-end 14th and 13th Gen K series of processors running into stability issues. As Intel's flagship chips, these parts come aggressively clocked in order to maximize performance through various implementations of boost and turbo, leaving them running close to their limits out of the box. But with high-end motherboards further goosing these chips to wring even more performance out of them, it would seem that the Intel desktop ecosystem has finally reached a tipping point where all of these efforts to boost performance have pushed these flagship chips to unstable conditions. To that end, Intel has released new gudiance to its consumer motherboard partners, strongly encouraging them to actually implment Intel's stock power settings, and to use those baseline settings as their out-of-the-box default.

While the underlying conditions are nothing new – we've published stories time and time again about motherboard features such as multi-core enhancement (MCE) and raised power consumption limits that seek to maximize how hard and how long systems are able to turbo boost – the issue has finally come to a head in the last couple of months thanks to accumulating reports of system instability with Intel's 13900K and 14900K processors. These instability problems are eventually solved by either tamping down on these motherboard performance-boosting features – bringing the chips back down to something closer to Intel's official operating parameters – or downclocking the chips entirely.

Intel first began publicly investigating the matter on the 27th of February, when Intel's Communications Manager, Thomas Hannaford, posted a thread on Intel's Community Product Support Forms titled "Regarding Reports of 13th/14th Gen Unlocked Desktop Users Experiencing Stability Issues". In this thread, Thomas Hannaford said, "Intel is aware of reports regarding Intel Core 13th and 14th Gen unlocked desktop processors experiencing issues with certain workloads. We're engaged with our partners and are conducting analysis of the reported issues. If you are experiencing these issues, please reach out to Intel Customer Support for further assistance in the interim."

Since that post went up, additional reports have been circulating about instability issues across various online forums and message boards. The underlying culprit has been theorized to be motherboards implementing an array of strategies to improve chip performance, including aggressive multi-core enhancement settings, "unlimited" PL2 turbo, and reduced load line calibration settings. At no point do any of these settings overclock a CPU and push it to a higher clockspeed than it's validated for, but these settings do everything possible to keep a chip at the highest clockspeed possible at all times – and in the process seem to have gone a step too far.

From "Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained"

We wrote a piece initially covering multi-core enhancement in 2012, detailing how motherboard manufacturers try to stay competitive with each other and leverage any headroom within the silicon to output the highest performance levels. And more recently, we've talked about how desktop systems with Intel chips are now regularly exceeding their rated TDPs – sometimes by extreme amounts – as motherboard vendors continue to push them to run as hard as possible for the best performance.

But things have changed since 2012. At the time, this wasn't so much of an issue, as overclocking was actually very favorable to increasing the performance of processors. But in 2024 with chips such as the Intel Core i9-14900K, we have CPUs shipping with a maximum turbo clock speed of 6.0 GHz and a peak power consumption of over 400 Watts, figures that were only a pipe dream a decade ago.

Jumping to the present time, over the weekend Intel released a statement about the matter to its partners, outlining their investigation so far and their sug... CPUs

From "Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained"

The Eurocom 780W AC Power Adapter Review: Big Power For Big Laptops While desktop PC power supplies receive the bulk of enthusiasts’ attention for good reasons – not the least of which being the vast selection of options that comes from being a standardized part – power supplies as a whole aren’t just a concern for big PCs. With the majority of PC sales having flipped to notebook sales some years ago, notebook power supplies already lead the market in volume. And while most laptops don’t need the kind of massively powered PSUs that dominate the desktop space, even that is slowly changing as desktop replacement-class laptops increasingly grow in performance and power consumption.

Perhaps the poster-child for the high-performance, high-powered laptop is Eurocom, who has a long history of developing heavy-duty DTR laptops that are all but portable desktop systems. Following recent trends in GPU power consumption and in GPU popularity for both gaming and AI workloads, the company has been selling a range of “mobile supercomputers”, which are practically large, tailor-made laptops that rival even the best of desktop computers – and have the power requirements to match.

In order to power their own high-end laptops, Eurocom has developed a rather unusual 780W AC adapter for high-performance laptops. Intended to power the most powerful of powerful laptops, their latest power adapter can supply over three-quarters of a kilowatt of DC power; a desktop-like wattage for a desktop-like device. It’s a laptop power adapter that’s unique in its scale, and with some room to scale up even further.

| Eurocom 780W AC Adapter Power specifications |

|

| RAIL | +20V |

| MAX OUTPUT | 39A |

| 780W | |

| DIMENSIONS | 325 x 110 x 40mm, 1.38kg |

| AC INPUT | 90 - 264 VAC, 50 - 60 Hz |

| MSRP | PSU: $299, Cable: $129+ |

Eurocom has offered this adapter for a few years now. But it’s taken on a new life as more laptops have been released that use such a large adapter (or two smaller 300W-ish power adapters). And, critically, Eurocom has made additional DC cable/connector sets for other manufactuers’ laptops, significantly increasing the number of systems it’s compatible with. Currently, Eurocom offers DC cables for the following laptops:

- Alienware M17x M18x; 1x DC Cable ; w/ barrel AW connector; 193cm/6.4ft

- Alienware AREA 51m; 1x DC Cable + Splitter Box w/ 2x barrel AW connectors; 152cm/5ft

- ASUS ROG G18 Strix; GX501V; GM501; GM501GM; GX531GM; 1x DC Cable; w/ barrel ROG connector

- ASUS G703GX, GZ700GX; 1x DC Cable w/ 2x ROG barrel connectors; 152cm/5ft

- CLEVO, OriginPC, Sager, XMG, EUROCOM laptops; 1x DC Cable; w/ 4-pin round connector; 182cm / 6ft

- CLEVO X370SNx; 1x DC Cable; w/ square connector; 120cm / 3.8ft

- CLEVO X170SM/X170KM; 1x DC Cable; w/ dual square connectors; 152cm / 5ft

- Dell Precision 7720/7710; 1x DC Cable; w/ barrel Dell connector; 120cm / 3.8ft

- MSI GE76, GT76, GT77, GE78HX Raider, Titan 18HX 1x DC Cable; w/ single square connector; 120cm / 3.8ft

- MSI laptops & MSI Trident AS Gaming Desktops; 1x DC Cable; w/ 4-pin round connector; 182cm / 6ft

The Eurocom 780W AC Adapter

Externally, the Eurocom 780W AC adapter looks like a hybrid between a PC PSU and a laptop adapter. It is shaped like an oversized laptop AC adapter but has a metallic body and cooling vents/fans. Eurocom advertises that it weighs “only 1.34kg”, which is the weight of an entire 14-inch laptop by comparison, but is relatively lightweight for a PSU with that kind of power output. The company logo is debossed across the top side of the adapter, with four round anti-slip pads found at its bottom. Care needs to be taken while moving it around because the metallic edges and weight can spell trouble for wooden surfaces.

Eurocom installed a small information display on the AC adapter, which shows the current, voltage, and power output, as well as the temperature of the adapter. It is not perfectly accur... Cases/Cooling/PSUs

Report: Seagate, Western Digital Hike HDD Prices Amid Surge In Demand Seagate Technology has reportedly notified its customers abouts its plans to raise prices on new hard drive orders and for demands that exceed prior agreements, echoing a similar move by Western Digital, which increased its prices earlier this month. These changes come in response to a surge in demand for high-capacity HDDs and constraints in supply due to decreased production capabilities of both Seagate and Western Digital, reports TrendForce.

According to industry insights reported by TechNews, the sector anticipates that the scarcity of high-capacity HDD products will persist throughout the current quarter and possibly extend over the entire year. It is forecasted that HDD prices will rise by 5% to 10% in Q2 2024 alone and could increase further as a reault of the ongoing challenges faced by the storage industry.

The primary driver behind Seagate's decision is increased demand for high-capacity HDDs, which are used to train AI models. This demand spike, coupled with a reduction in production output from hard drive makers, has created a significant supply-demand imbalance. As a result, Seagate has decided to adjust their pricing strategy to manage the situation. Further exacerbating the issue are global inflationary pressures which continue to inflate costs across the board, which also contributed to the company's decision to increase prices, Seagate said in a message to clients published by TrendForce.

Seagate emphasized that its reduced production capacity has been a major challenge, hindering the company's ability to fulfill customer demands fully and promptly.

"As a result, we will be implementing price increases effective immediately on new orders and for demand that is over and above previously committed volumes," the alleged memo from Seagate reads. "Supply constraints are expected to continue and as such we anticipate that prices will continue to increase in the coming quarters."

Earlier this month Western Digital also informed its customers about price hikes for its HDD and SSD products. This notification was based on similar issues — higher than anticipated demand across the whole product range and additional supply chain challenges affecting the electronics sector. Western Digital's announcement made it clear that these disruptions are likely to continue, prompting further price adjustments.

Sources: TrendForce, TrendForce, TechNews

Storage

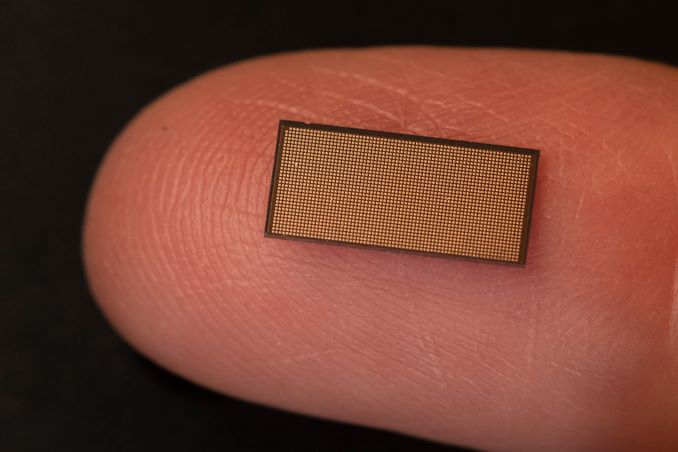

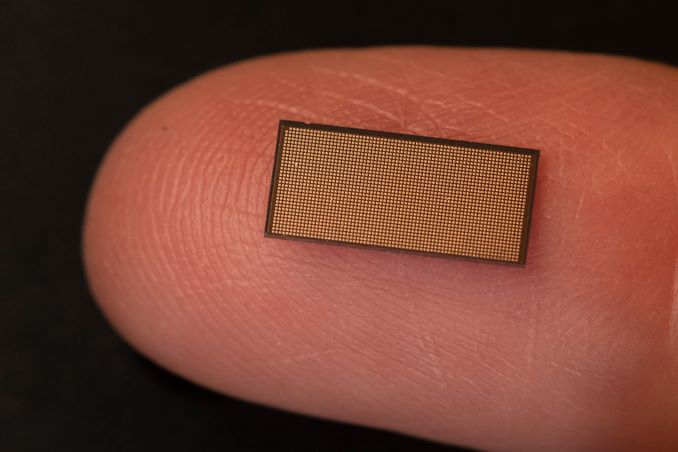

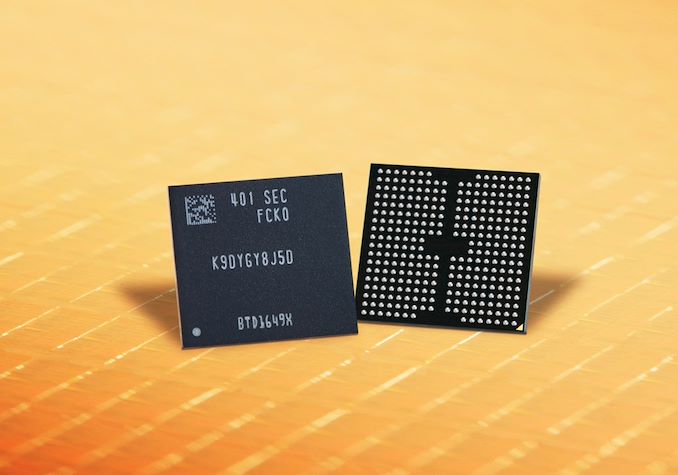

Samsung Starts Mass Production of 9th Generation V-NAND: 1Tb 3D TLC NAND Samsung Electronics has started mass production of its 9th generation of V-NAND memory. The first dies based on their latest NAND tech come in a 1 Tb capacity using a triple-level cell (TLC) architecture, with data transfer rates as high as 3.2 GT/s. The new 3D TLC NAND memory will initially be used to build high-capacity and high-performance SSDs, which will help to solidify Samsung's position in the storage market.

Diving right in, Samsung is conspicuously avoiding to list the number of layers in their latest generation NAND, which is the principle driving factor in increasing capacity generation-on-generation. The company's current 8th gen V-NAND is 236 layers – similar to its major competitors – and word on the street is that 9th gen V-NAND ups that to 290 layers, though this remains to be confirmed.

Regardless, Samsung says that its 9th generation V-NAND memory boasts an approximate 50% improvement in bit density over its 8th generation predecessor. Driving this gains, the company cites the miniaturization of the cell size, as well as the integration of enhanced memory cell technologies that reduce interference and extend the lifespan of the cells. With their latest NAND technology, Samsung has also been able to eliminate dummy channel holes, thus reducing the planar area of the memory cells.

Interestingly, today's announcement also marks the first time that Samsung has publicly confirmed their use of string stacking in their NAND, referring to it as their "double-stack structure." The company is widely believed to have been using sting stacking back in their 8th generation NAND as well, however this was never confirmed by the company. Regardless, the use of string stacking is only going to increase from here, as vendors look to keep adding layers to their NAND dies, while manufacturing variability and channel hole tolerances make it difficult to produce more than 150-200 layers in a single stack.

| Samsung TLC V- NAND Flash Memory | ||

| 9th Gen V-NAND | 8th Gen V-NAND | |

| Layers | 290? | 236 |

| Decks | 2 (x145) | 2 (x118) |

| Die Capacity | 1 Tbit | 1 Tbit |

| Die Size (mm2) | ?mm2 | ?mm2 |

| Density (Gbit/mm2) | ? | ? |

| I/O Speed | 3.2 GT/s (Toggle 5.1) |

2.4 GT/s (Toggle 5.0) |

| Planes | 6? | 4 |

| CuA / PuC | Yes | Yes |

Speaking of channel holes, another key technological enhancement in the 9th gen V-NAND is Samsung's advanced 'channel hole etching' technology. This process improves manufacturing productivity by enabling the simultaneous creation of electron pathways within a double-stack structure. This method is crucial as it enables efficient drilling through more layers, which is increasingly important as cell layers are added.

The latest V-NAND also features the introduction of a faster NAND flash interface, Toggle DDR 5.1, which boosts peak data transfer rates by 33% to 3.2 GT/s, or almost 400MB/sec for a single die. Additionally, 9th gen V-NAND's power consumption has been reduced by 10%, according to Samsung. Though Samsung doesn't state under what conditions – presumably, this is at iso-frequency rather than max frequency.

Samsung's launch of 1Tb TLC V-NAND is set to be followed by the release of a quad-level cell (QLC) model later this year.

"We are excited to deliver the industry’s first 9th-gen V-NAND which will bring future... SSDs

Qualcomm Intros Snapdragon X Plus, Details Complete Snapdragon X Launch Day Chip Stack As Qualcomm prepares for the mid-year launch of their forthcoming Snapdragon X SoCs for PCs, and the eagerly anticipated Oryon CPU cores within, the company is finally shoring up their official product plans, and releasing some additional technical details in the process. Thus far the company has been demonstrating their Snapdragon X Elite SoC in its highest-performing, fully-enabled configuration. But the retail Snapdragon X Elite will not be a single part; instead, Qualcomm is preparing a whole range of chip configurations for various price/performance tiers in the market. Altogether, there will be 3 Snapdragon X Elite SKUs that differ in CPU and GPU performance.

As well, the company is introducing a second Snapdragon X tier, Snapdragon X Plus, for those SKUs positioned below the Elite performance tier. As of today, this will be a single configuration. But if the Snapdragon X lineup is successful and demand warrants it, I would not be surprised to see Qualcomm expand it further – as they have certainly left themselves the room for it in their product stack. In the meantime, with Qualcomm’s expected launch competition now shipping (Intel Core Ultra Meteor Lake and AMD Ryzen Mobile 8040 Hawk Point), the company is also very confident that even these reduced performance Snapdragon X Plus chips will be able to beat Intel and AMD in multithreaded performance – never mind the top-tier Snapdragon X Elite chips.

Qualcomm will be launching this expanded four chip stack at once; so both Snapdragon X Elite and Snapdragon X Plus tier devices should be available at the same time. The company’s goal is still to have devices on the shelf “mid-year”, although the company isn’t providing any more precise guidance than that. With Qualcomm’s CEO, Cristiano Amon, set to deliver a Computex keynote in June, I expect we’ll get more specific details on timings then, along with the company and its partners using the event to announce and showcase some retail laptop designs. So this is very much looking like a summer launch at the moment.

In the meantime, Qualcomm is already showing off what their Snapdragon X Plus chips can do with a fresh set of live benchmarks, akin to their Snapdragon X Elite performance previews from October 2023. We’ll dive into those in a bit, but suffice it to say, Qualcomm knows the score, and they want to make sure the entire world knows when they’re winning.

CPUs

Qualcomm Intros Snapdragon X Plus, Details Complete Snapdragon X Launch Day Chip Stack As Qualcomm prepares for the mid-year launch of their forthcoming Snapdragon X SoCs for PCs, and the eagerly anticipated Oryon CPU cores within, the company is finally shoring up their official product plans, and releasing some additional technical details in the process. Thus far the company has been demonstrating their Snapdragon X Elite SoC in its highest-performing, fully-enabled configuration. But the retail Snapdragon X Elite will not be a single part; instead, Qualcomm is preparing a whole range of chip configurations for various price/performance tiers in the market. Altogether, there will be 3 Snapdragon X Elite SKUs that differ in CPU and GPU performance.

As well, the company is introducing a second Snapdragon X tier, Snapdragon X Plus, for those SKUs positioned below the Elite performance tier. As of today, this will be a single configuration. But if the Snapdragon X lineup is successful and demand warrants it, I would not be surprised to see Qualcomm expand it further – as they have certainly left themselves the room for it in their product stack. In the meantime, with Qualcomm’s expected launch competition now shipping (Intel Core Ultra Meteor Lake and AMD Ryzen Mobile 8040 Hawk Point), the company is also very confident that even these reduced performance Snapdragon X Plus chips will be able to beat Intel and AMD in multithreaded performance – never mind the top-tier Snapdragon X Elite chips.

Qualcomm will be launching this expanded four chip stack at once; so both Snapdragon X Elite and Snapdragon X Plus tier devices should be available at the same time. The company’s goal is still to have devices on the shelf “mid-year”, although the company isn’t providing any more precise guidance than that. With Qualcomm’s CEO, Cristiano Amon, set to deliver a Computex keynote in June, I expect we’ll get more specific details on timings then, along with the company and its partners using the event to announce and showcase some retail laptop designs. So this is very much looking like a summer launch at the moment.

In the meantime, Qualcomm is already showing off what their Snapdragon X Plus chips can do with a fresh set of live benchmarks, akin to their Snapdragon X Elite performance previews from October 2023. We’ll dive into those in a bit, but suffice it to say, Qualcomm knows the score, and they want to make sure the entire world knows when they’re winning.

CPUs

Seagate: Mozaic 3+ HAMR Hard Drives Can Last Over Seven Years As Seagate ramps up shipments of its new heat assisted magnetic recording (HAMR)-based Mozaic 3+ hard drive platform, the company is both in the enviable position of shipping the first major new hard drive technology in a decade, and the much less enviable position of proving the reliability of the first major new hard drive technology in a decade. Due to HAMR's use of temporal heating with its platters, as well as all-new read/write heads, HAMR introduces multiple new changes at once that have raise questions about how reliable the technology will be. Looking to address these matters (and further promote their HAMR drives), Seagate has published a fresh blog post outlining the company's R&D efforts, and why the company expects their HAMR drives to last several years – as long or longer than current PMR hard drives.

According to the company, the reliability of Mozaic 3+ drives on par with traditional drives relying on perpendicular magnetic recording (PMR), the company says. In fact, components of HAMR HDDs have demonstrated a 50% increase in reliability over the past two years. Seagate says that Mozaic 3+ drives boast impressive durability metrics: their read/write heads have demonstrated capacity to handle over 3.2 petabytes of data transfer over 6,000 hours of operation, which exceeds data transfers of typical nearline hard drives by 20 times. Accordingly, Seagate is rating these drives for a mean time between failure (MTBF) 2.5 million hours, which is in-line with PMR-based drives.

Based on their field stress tests, involving over 500,000 Mozaic 3+ drives, Seagate says that the heads of Mozaic 3+ drives will last over seven years, surpassing the typical lifespan of current PMR-based drives. Generally, customers anticipate that modern PMR drives will last between four and five years with average usage, so these drives would exceed current expectations.

Altogether, Seagate is continuing aim for a seamless transition from PMR to HAMR drives in customer systems. That means ensuring that these new drives can fit into existing data center infrastructures without requiring any changes to enterprise specifications, warranty conditions, or form factors.

Storage

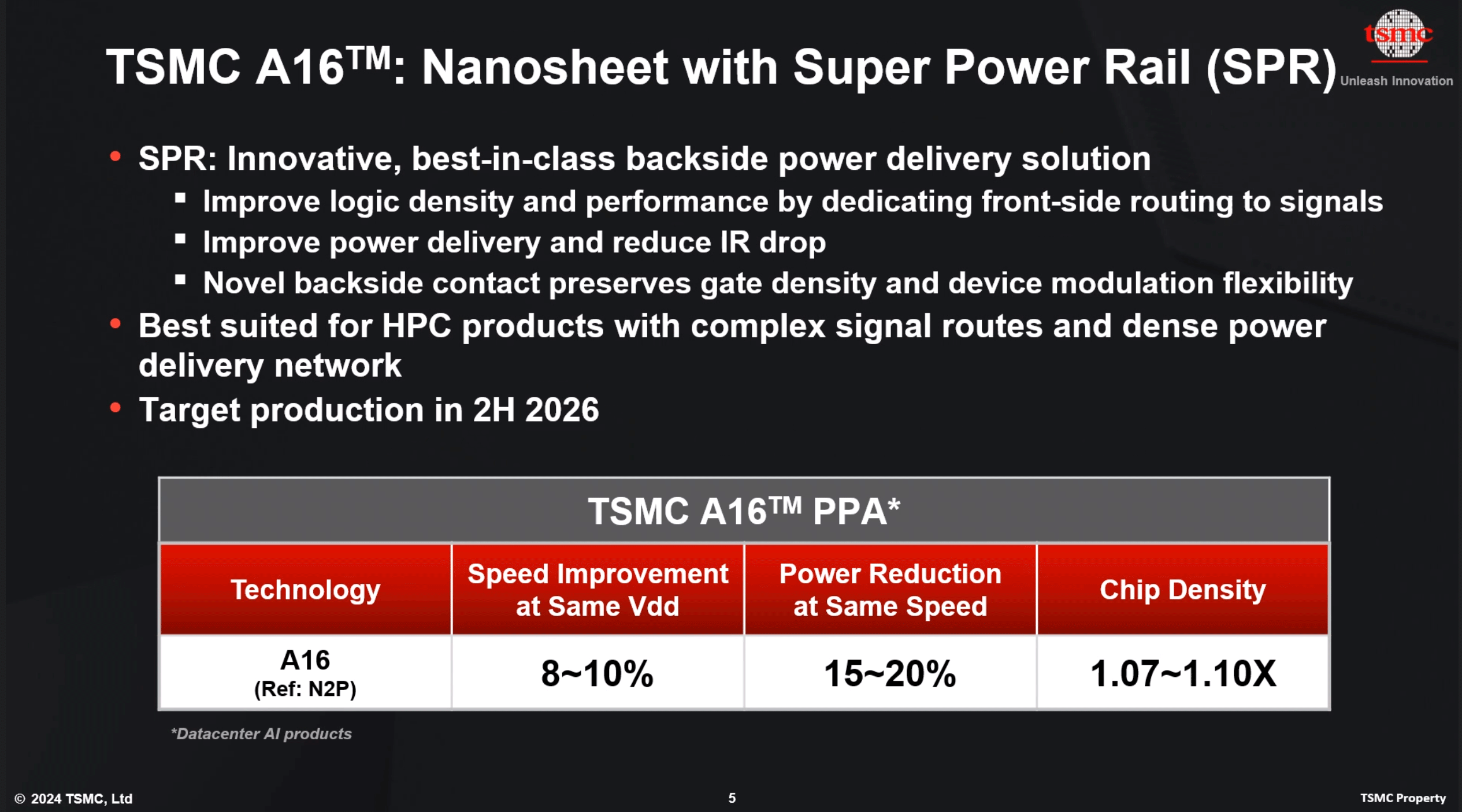

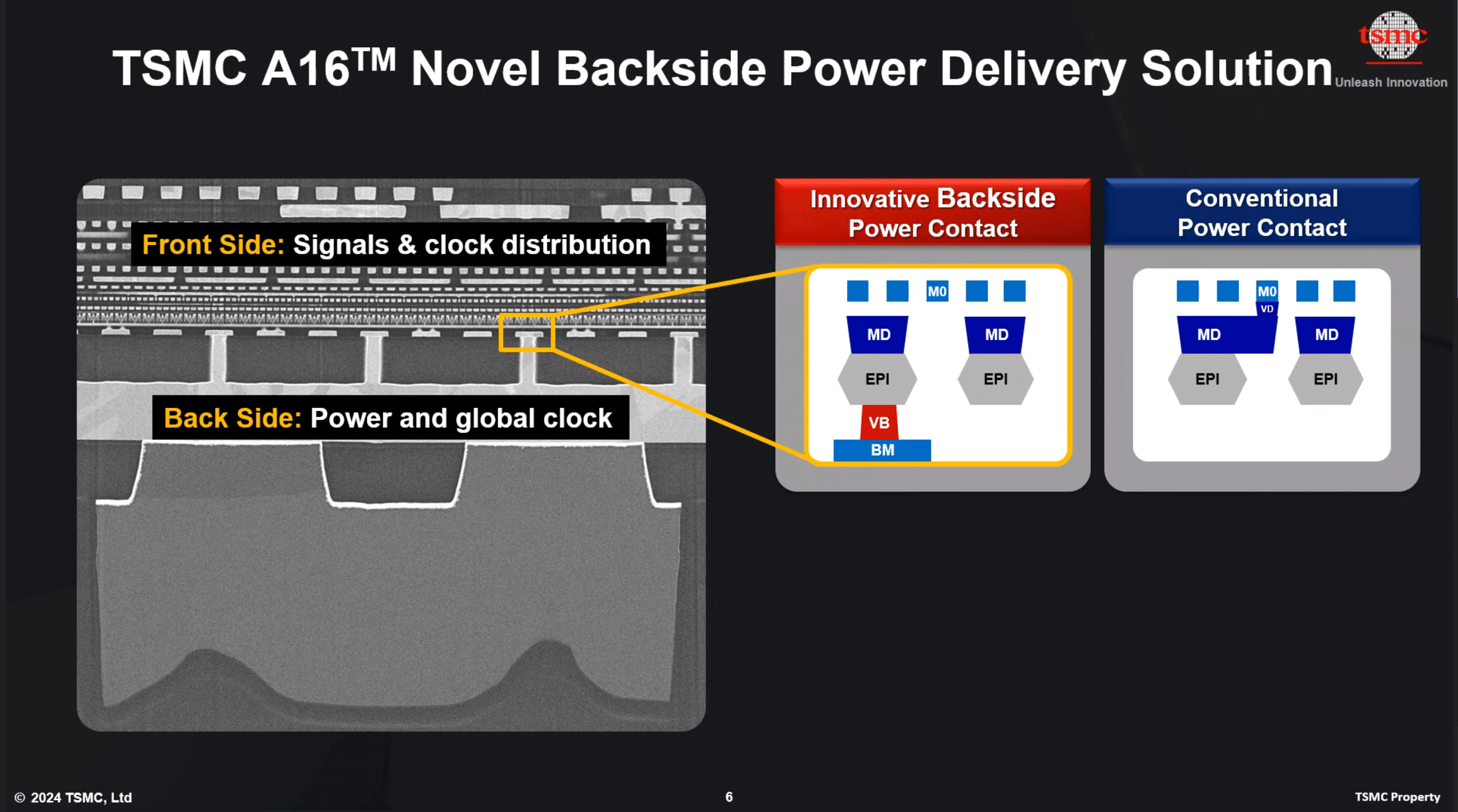

TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power With the arrival of spring comes showers, flowers, and in the technology industry, TSMC's annual technology symposium series. With customers spread all around the world, the Taiwanese pure play foundry has adopted an interesting strategy for updating its customers on its fab plans, holding a series of symposiums from Silicon Valley to Shanghai. Kicking off the series every year – and giving us our first real look at TSMC's updated foundry plans for the coming years – is the Santa Clara stop, where yesterday the company has detailed several new technologies, ranging from more advanced lithography processes to massive, wafer-scale chip packing options.

Today we're publishing several stories based on TSMC's different offerings, starting with TSMC's marquee announcement: their A16 process node. Meanwhile, for the rest of our symposium stories, please be sure to check out the related reading below, and check back for additional stories.

- TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power

- TSMC 2nm Update: N2 In 2025, N2P Loses Backside Power, and NanoFlex Brings Optimal Cells

- TSMC Preps Cheaper 4nm N4C Process For 2025, Aiming For 8.5% Cost Reduction

- TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips

- TSMC Jumps Into Silicon Photonics, Lays Out Roadmap For 12.8 Tbps COUPE On-Package Interconnect

- TSMC Readies 8x Reticle Super Carrier Interposer For Next-Gen Chips Twice as Large As Today's

Headlining its Silicon Valley stop, TSMC announced its first 'angstrom-class' process technology: A16. Following a production schedule shift that has seen backside power delivery network technology (BSPDN) removed from TSMC's N2P node, the new 1.6nm-class production node will now be the first process to introduce BSPDN to TSMC's chipmaking repertoire. With the addition of backside power capabilities and other improvements, TSMC expects A16 to offer significantly improved performance and energy efficiency compared to TSMC's N2P fabrication process. It will be available to TSMC's clients starting H2 2026.

TSMC A16: Combining GAAFET With Backside Power Delivery

At a high level, TSMC's A16 process technology will rely on gate-all-around (GAAFET) nanosheet transistors and will feature a backside power rail, which will both improve power delivery and moderately increase transistor density. Compared to TSMC's N2P fabrication process, A16 is expected to offer a performance improvement of 8% to 10% at the same voltage and complexity, or a 15% to 20% reduction in power consumption at the same frequency and transistor count. TSMC is not listing detailed density parameters this far out, but the company says that chip density will increase by 1.07x to 1.10x – keeping in mind that transistor density heavily depends on the type and libraries of transistors used.

The key innovation of TSMC's A16 node, is its Super Power Rail (SPR) backside power delivery network, a first for TSMC. The contract chipmaker claims that A16's SPR is specifically tailored for high-performance computing products that feature both complex signal routes and dense power circuitry.

As noted earlier, with this week's announcement, A16 has now become the launch vehicle for backside power delivery at TSMC. The company was initially slated to offer BSPDN technology with N2P in 2026, but for reasons that aren't entirely clear, the tech has been punted from N2P and moved to A16. TSMC's official timing for N2P in 2023 was always a bit loose, so it's hard to say if this represents much of a practical delay for BSPDN at TSMC. But at the same time, it's important to underscore that A16 isn't just N2P renamed, but rather it will be a di... Semiconductors

Report: Seagate, Western Digital Hike HDD Prices Amid Surge In Demand Seagate Technology has reportedly notified its customers abouts its plans to raise prices on new hard drive orders and for demands that exceed prior agreements, echoing a similar move by Western Digital, which increased its prices earlier this month. These changes come in response to a surge in demand for high-capacity HDDs and constraints in supply due to decreased production capabilities of both Seagate and Western Digital, reports TrendForce.

According to industry insights reported by TechNews, the sector anticipates that the scarcity of high-capacity HDD products will persist throughout the current quarter and possibly extend over the entire year. It is forecasted that HDD prices will rise by 5% to 10% in Q2 2024 alone and could increase further as a reault of the ongoing challenges faced by the storage industry.

The primary driver behind Seagate's decision is increased demand for high-capacity HDDs, which are used to train AI models. This demand spike, coupled with a reduction in production output from hard drive makers, has created a significant supply-demand imbalance. As a result, Seagate has decided to adjust their pricing strategy to manage the situation. Further exacerbating the issue are global inflationary pressures which continue to inflate costs across the board, which also contributed to the company's decision to increase prices, Seagate said in a message to clients published by TrendForce.

Seagate emphasized that its reduced production capacity has been a major challenge, hindering the company's ability to fulfill customer demands fully and promptly.

"As a result, we will be implementing price increases effective immediately on new orders and for demand that is over and above previously committed volumes," the alleged memo from Seagate reads. "Supply constraints are expected to continue and as such we anticipate that prices will continue to increase in the coming quarters."

Earlier this month Western Digital also informed its customers about price hikes for its HDD and SSD products. This notification was based on similar issues — higher than anticipated demand across the whole product range and additional supply chain challenges affecting the electronics sector. Western Digital's announcement made it clear that these disruptions are likely to continue, prompting further price adjustments.

Sources: TrendForce, TrendForce, TechNews

Storage

Samsung To Receive $6.4 Billion Under CHIPS Act to Build $40 Billion Fab in Texas Samsung Electronics this week was awarded up to $6.4 billion from the U.S. government under the CHIPS and Science Act to build its new fab complex in Taylor, Texas. This is the third major award under the act in the last month, with all three leading-edge fabs – Intel, TSMC, and now Samsung – receiving multi-billion dollar funding packages under the domestic chip production program. Overall, the final price tag on Samsung's new fab complex is expected to reach $40 billion by the time it's completed later this decade.

Samsung's CHIPS Act funding was announced during a celebratory event attended by U.S. Secretary of Commerce Gina Raimondo and Samsung Semiconductor chief executive Kye Hyun Kyung. During the event, Kyung outlined the strategic goals of the expansion, emphasizing that the additional funding will not only increase production capacity but also strengthen the entire local semiconductor ecosystem. Samsung plans to equip its fab near Taylor, Texas, with the latest wafer fab tools to produce advanced chips. The Financial Times reports that Samsung aims to produce semiconductors on its 2nm-class process technology starting 2026, though for now this is unofficial information.

"I am pleased to announce a preliminary agreement between Samsung and the Department of Commerce to bring Samsung's advanced semiconductor manufacturing and research and development to Texas," said Joe Biden, the U.S. president, in a statement. "This announcement will unleash over $40 billion in investment from Samsung, and cement central Texas's role as a state-of-the-art semiconductor ecosystem, creating at least 21,500 jobs and leveraging up to $40 million in CHIPS funding to train and develop the local workforce. These facilities will support the production of some of the most powerful chips in the world, which are essential to advanced technologies like artificial intelligence and will bolster U.S. national security."

Samsung has been a significant contributor to the Texas economy for decades, starting chip manufacturing in the U.S. in 1996. With previous investments totaling $18 billion in its Austin operations, Samsung's expansion into Taylor with an additional investment of at least $17 billion underscores its role as one of the largest foreign direct investors in U.S. history. The total expected investment in the new fab surpasses $40 billion, making it one of the largest for a greenfield project in the nation and transforming Taylor into a major hub for semiconductor manufacturing.

The CEO highlighted the substantial economic impact of Samsung's operations, noting a nearly double increase in regional economic output from $13.6 billion to $26.8 billion between 2022 and 2023. The ongoing expansion is projected to further stimulate economic growth, create thousands of jobs, and enhance the community's overall development.

“We are not just expanding production facilities; we’re strengthening the local semiconductor ecosystem and positioning the U.S. as a global semiconductor manufacturing destination.” said Kyung. “To meet the expected surge in demand from U.S. customers, for future products like AI chips, our fabs will be equipped for cutting-edge process technologies and help bring security to the U.S. semiconductor supply chain.”

Samsung is also committed to environmental sustainability and workforce development. The company plans to operate using 100% clean energy and incorporate advanced water management technologies. Additionally, it is investing in education and training programs to develop a new generation of semiconductor professionals. These initiatives include partnerships with educational institutions and programs tailored for military veterans.

In his remarks, Kyung expressed gratitude to President Biden, Secretary Raimondo, and other governmental and community supporters for their ongoing support. This collaborative effort between Samsung and various levels of government, as well as the local community, is pivotal in advancing America's... Semiconductors

AMD Quietly Launches Ryzen 7 8700F and Ryzen 5 8400F Processors AMD has recently expanded its Ryzen 8000 series by introducing the Ryzen 7 8700F and Ryzen 5 8400F processors. Initially launched in China, these chips were added to AMD's global website, signaling they are available worldwide, apparently from April 1st. Built from the recent Zen 4-based Phoenix APUs using the TSMC 4nm node as their Zen 4 mobile chips, these new CPUs lack integrated graphics. However, the Ryzen 7 8700F does include the integrated Ryzen AI NPU for added capabilities in a world currently dominated by AI and moving it directly into the PC.

The company's decision to announce these chips in China aligns with its strategy to offer Ryzen solutions at every price point in the market. Although AMD didn't initially disclose the full specifications of these F-series models, and we did reach out to the company to ask about them, they refused to discuss them with us. Their listing on the website has now been updated with a complete list of specifications and features, with everything but the price mentioned.

| AMD Ryzen 8000G vs. Ryzen 8000F Series (Desktop) Zen 4 (Phoenix) |

|||||||||

| AnandTech | Cores/Threads | Base Freq |

Turbo Freq |

GPU | GPU Freq |

Ryzen AI (NPU) |

L3 Cache (MB) |

TDP | MSRP |

| Ryzen 7 | |||||||||

| Ryzen 7 8700G | 8/16 | 4200 | 5100 | R780M 12 CUs |

2900 | Y | 16 | 65W | $329 |

| Ryzen 7 8700F | 8/16 | 4100 | 5000 | - | - | Y | 16 | 65W | ? |

| Ryzen 5 | |||||||||

| Ryzen 5 8600G | 6/12 | 4300 | 5000 | R760M 8 CUs |

2800 | Y | 16 | 65W | $229 |

| Ryzen 5 8400F | 6/12 | 4200 | 4700 | - | - | N | 16 | 65W | ? |

The Ryzen 7 8700F features an 8C/16T design, with 16MB of L3 cache and the same 65W TDP as the Ryzen 7 8700G. Although the base clock speed is 4.1 GHz, it boosts to 5.0 GHz; this is 100 MHz less on both base/boost clocks than the 8700G. Meanwhile, the Ryzen 5 8400F is a slightly scaled-down version of the Ryzen 8600G APU, with 6C/12, 16MB of L3 cache, and again has a 100 MHz reduction to base clocks compared to the 8600G. Unlike the Ryzen 5 8400F, the Ryzen 7 8700F keeps AMD's Ryzen AI NPU, adding additional capability for generative AI.

The Ryzen 5 8400F can boost up to 4.7 GHz, 300 MHz slower than the Ryzen 5 8600G. AMD also allows overclocking for these new F-series chips, which means users could potentially boost the performance of these processors to match their G-series equivalents.

Pricing details are still pending, but to remain competitive, AMD will likely need to price these CPUs below the 8700G and 8600G, as well as the Ryzen 7 7700 and Ryzen 5 7600. These CPUs offer, albeit very limited, integrated graphics and have double the L3 cache capacity, along with higher boost clocks than the 8000F series chips, so pricing is something to consider whenever pricing becomes available.

CPUs

Corsair Enters Workstation Memory Market with WS Series XMP/EXPO DDR5 RDIMMs Corsair has introduced a family of registered memory modules with ECC that are designed for AMD's Ryzen Threadripper 7000 and Intel's Xeon W-2400/3400-series processors. The new Corsair WS DDR5 RDIMMs with AMD EXPO and Intel XMP 3.0 profiles will be available in kits of up to 256 GB capacity and at speeds of up to 6400 MT/s.

Corsair's family of WS DDR5 RDIMMs includes 16 GB modules operating at up to 6400 MT/s with CL32 latency as well as 32 GB modules functioning at 5600 MT/s with CL40 latency. At present, Corsair offers a quad-channel 64 GB kit (4×16GB, up to 6400 MT/s), a quad-channel 128GB kit (4×32GB, 5600 MT/s), an eight-channel 128 GB kit (8×16GB, 5600 MT/s), and an eight-channel 256 GB kit (8×32GB, 5600 MT/s) and it remains to be seen whether the company will expand the lineup.

Corsair's WS DDR5 RDIMMs are designed for AMD's TRX50 and WRX90 platforms as well as Intel's W790 platform and are therefore compatible with AMD's Ryzen Threadripper Pro 7000 and 7000WX-series as well as Intel's Xeon W-2400/3400-series CPUs. The modules feature both AMD EXPO and Intel XMP 3.0 profiles to easily set their beyond-JEDEC-spec settings and come with thin heat spreaders made of pyrolytic graphite sheet (PGS), which thermal conductivity than that of copper and aluminum of the same thickness. For now, Corsair does not disclose which RCD and memory chips its registered memory modules use.

Unlike many of its rivals among leading DIMM manufacturers, Corsair did not introduce its enthusiast-grade RDIMMs when AMD and Intel released their Ryzen Threadripper and Xeon W-series platforms for extreme workstations last year. It is hard to tell what the reason for that is, but perhaps the company wanted to gain experience working with modules featuring registered clock drivers (RCDs) as well as AMD's and Intel's platforms for extreme workstations.

The result of the delay looks to be quite rewarding: unlike modules from its competitors that either feature AMD EXPO or Intel XMP 3.0 profiles, Corsair's WS DDR5 RDIMMs come with both. While this may not be important on the DIY market where people know exactly what they are buying for their platform, this is a great feature for system integrators, which can use Corsair WS DDR5 RDIMMs both for their AMD Ryzen Threadripper and Intel Xeon W-series builds, something that greatly simplifies their inventory management.

Since Corsair's WS DDR5 RDIMMs are aimed at workstations and are tested to offer reliable performance beyond JEDEC specifications, they are quite expensive. The cheapest 64 GB DDR5-5600 CL40 kit costs $450, the fastest 64 GB DDR5-6400 CL32 kit is priced at $460, whereas the highest end 256 GB DDR5-5600 CL40 kit is priced at $1,290.

Memory

In Light of Stability Concerns, Intel Issues Request to Motherboards Vendors to Actually Follow Stock Power Settings Across the internet, from online forums such as Reddit to various other tech media outlets, there's a lot of furor around reports of Intel's top-end 14th and 13th Gen K series of processors running into stability issues. As Intel's flagship chips, these parts come aggressively clocked in order to maximize performance through various implementations of boost and turbo, leaving them running close to their limits out of the box. But with high-end motherboards further goosing these chips to wring even more performance out of them, it would seem that the Intel desktop ecosystem has finally reached a tipping point where all of these efforts to boost performance have pushed these flagship chips to unstable conditions. To that end, Intel has released new gudiance to its consumer motherboard partners, strongly encouraging them to actually implment Intel's stock power settings, and to use those baseline settings as their out-of-the-box default.

While the underlying conditions are nothing new – we've published stories time and time again about motherboard features such as multi-core enhancement (MCE) and raised power consumption limits that seek to maximize how hard and how long systems are able to turbo boost – the issue has finally come to a head in the last couple of months thanks to accumulating reports of system instability with Intel's 13900K and 14900K processors. These instability problems are eventually solved by either tamping down on these motherboard performance-boosting features – bringing the chips back down to something closer to Intel's official operating parameters – or downclocking the chips entirely.

Intel first began publicly investigating the matter on the 27th of February, when Intel's Communications Manager, Thomas Hannaford, posted a thread on Intel's Community Product Support Forms titled "Regarding Reports of 13th/14th Gen Unlocked Desktop Users Experiencing Stability Issues". In this thread, Thomas Hannaford said, "Intel is aware of reports regarding Intel Core 13th and 14th Gen unlocked desktop processors experiencing issues with certain workloads. We're engaged with our partners and are conducting analysis of the reported issues. If you are experiencing these issues, please reach out to Intel Customer Support for further assistance in the interim."

Since that post went up, additional reports have been circulating about instability issues across various online forums and message boards. The underlying culprit has been theorized to be motherboards implementing an array of strategies to improve chip performance, including aggressive multi-core enhancement settings, "unlimited" PL2 turbo, and reduced load line calibration settings. At no point do any of these settings overclock a CPU and push it to a higher clockspeed than it's validated for, but these settings do everything possible to keep a chip at the highest clockspeed possible at all times – and in the process seem to have gone a step too far.

From "Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained"

We wrote a piece initially covering multi-core enhancement in 2012, detailing how motherboard manufacturers try to stay competitive with each other and leverage any headroom within the silicon to output the highest performance levels. And more recently, we've talked about how desktop systems with Intel chips are now regularly exceeding their rated TDPs – sometimes by extreme amounts – as motherboard vendors continue to push them to run as hard as possible for the best performance.

But things have changed since 2012. At the time, this wasn't so much of an issue, as overclocking was actually very favorable to increasing the performance of processors. But in 2024 with chips such as the Intel Core i9-14900K, we have CPUs shipping with a maximum turbo clock speed of 6.0 GHz and a peak power consumption of over 400 Watts, figures that were only a pipe dream a decade ago.

Jumping to the present time, over the weekend Intel released a statement about the matter to its partners, outlining their investigation so far and their sug... CPUs

From "Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained"

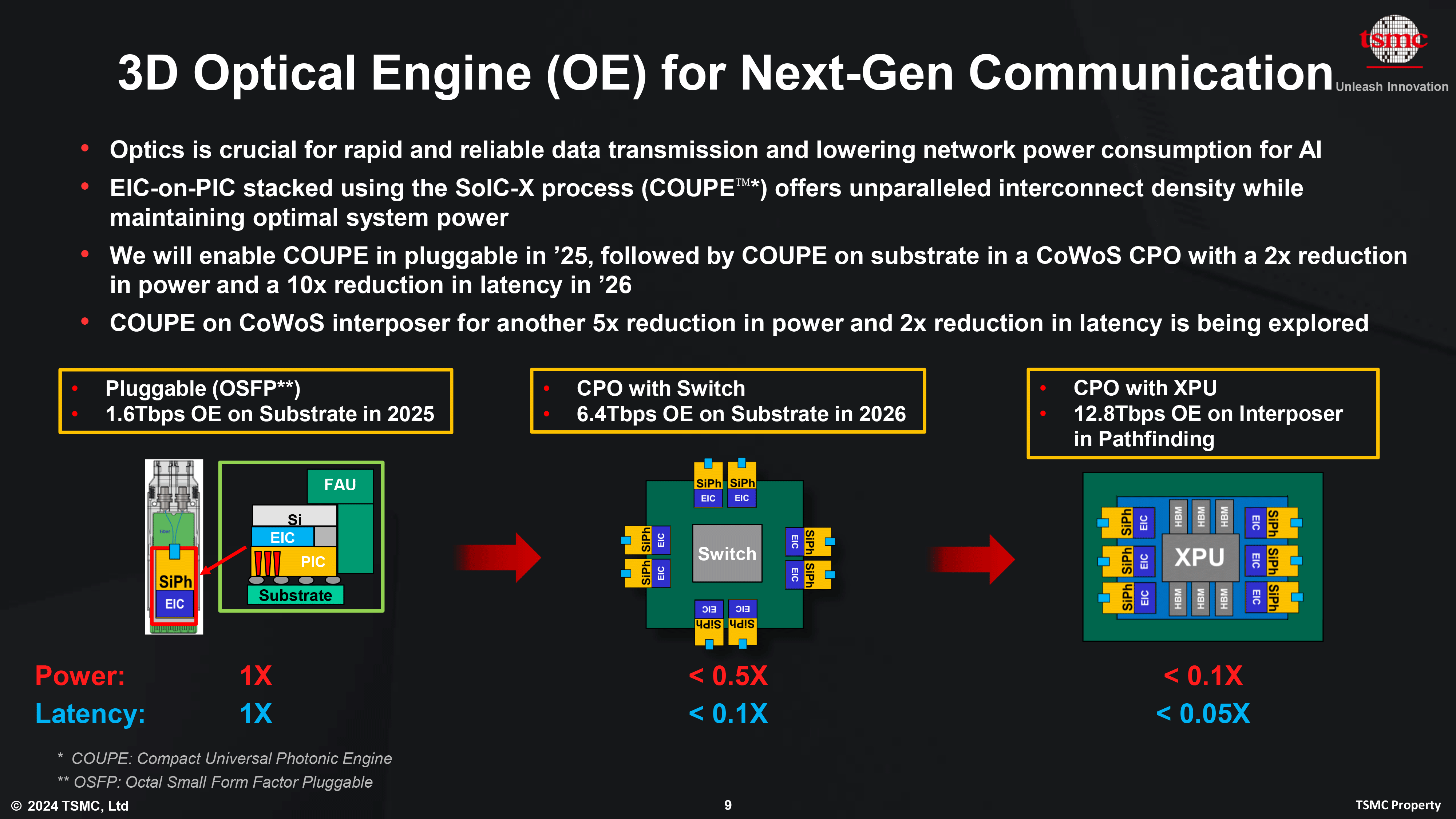

TSMC Jumps Into Silicon Photonics, Lays Out Roadmap For 12.8 Tbps COUPE On-Package Interconnect Optical connectivity – and especially silicon photonics – is expected to become a crucial technology to enable connectivity for next-generation datacenters, particularly those designed HPC applications. With ever-increasing bandwidth requirements needed to keep up with (and keep scaling out) system performance, copper signaling alone won't be enough to keep up. To that end, several companies are developing silicon photonics solutions, including fab providers like TSMC, who this week outlined its 3D Optical Engine roadmap as part of its 2024 North American Technology Symposium, laying out its plan to bring up to 12.8 Tbps optical connectivity to TSMC-fabbed processors.

TSMC's Compact Universal Photonic Engine (COUPE) stacks an electronics integrated circuit on photonic integrated circuit (EIC-on-PIC) using the company's SoIC-X packaging technology. The foundry says that usage of its SoIC-X enables the lowest impedance at the die-to-die interface and therefore the highest energy efficiency. The EIC itself is produced at a 65nm-class process technology.

TSMC's 1st Generation 3D Optical Engine (or COUPE) will be integrated into an OSFP pluggable device running at 1.6 Tbps. That's a transfer rate well ahead of current copper Ethernet standards – which top out at 800 Gbps – underscoring the immediate bandwidth advantage of optical interconnects for heavily-networked compute clusters, never mind the expected power savings.

Looking further ahead, the 2nd Generation of COUPE is designed to integrate into CoWoS packaging as co-packaged optics with a switch, allowing optical interconnections to be brought to the motherboard level. This version COUPE will support data transfer rates of up to 6.40 Tbps with reduced latency compared to the first version.

TSMC's third iteration of COUPE – COUPE running on a CoWoS interposer – is projected to improve on things one step further, increasing transfer rates to 12.8 Tbps while bringing optical connectivity even closer to the processor itself. At present, COUPE-on-CoWoS is in the pathfinding stage of development and TSMC does not have a target date set.

Ultimately, unlike many of its industry peers, TSMC has not participated in the silicon photonics market up until now, leaving this to players like GlobalFoundries. But with its 3D Optical Engine Strategy, the company will enter this important market as it looks to make up for lost time.

Related Reading

- TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power

- TSMC 2nm Update: N2 In 2025, N2P Loses Backside Power, and NanoFlex Brings Optimal Cells

- TSMC Preps Cheaper 4nm N4C Process For 2025, Aiming For 8.5% Cost Reduction

- TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips

Semiconductors

Seagate: Mozaic 3+ HAMR Hard Drives Can Last Over Seven Years As Seagate ramps up shipments of its new heat assisted magnetic recording (HAMR)-based Mozaic 3+ hard drive platform, the company is both in the enviable position of shipping the first major new hard drive technology in a decade, and the much less enviable position of proving the reliability of the first major new hard drive technology in a decade. Due to HAMR's use of temporal heating with its platters, as well as all-new read/write heads, HAMR introduces multiple new changes at once that have raise questions about how reliable the technology will be. Looking to address these matters (and further promote their HAMR drives), Seagate has published a fresh blog post outlining the company's R&D efforts, and why the company expects their HAMR drives to last several years – as long or longer than current PMR hard drives.

According to the company, the reliability of Mozaic 3+ drives on par with traditional drives relying on perpendicular magnetic recording (PMR), the company says. In fact, components of HAMR HDDs have demonstrated a 50% increase in reliability over the past two years. Seagate says that Mozaic 3+ drives boast impressive durability metrics: their read/write heads have demonstrated capacity to handle over 3.2 petabytes of data transfer over 6,000 hours of operation, which exceeds data transfers of typical nearline hard drives by 20 times. Accordingly, Seagate is rating these drives for a mean time between failure (MTBF) 2.5 million hours, which is in-line with PMR-based drives.

Based on their field stress tests, involving over 500,000 Mozaic 3+ drives, Seagate says that the heads of Mozaic 3+ drives will last over seven years, surpassing the typical lifespan of current PMR-based drives. Generally, customers anticipate that modern PMR drives will last between four and five years with average usage, so these drives would exceed current expectations.

Altogether, Seagate is continuing aim for a seamless transition from PMR to HAMR drives in customer systems. That means ensuring that these new drives can fit into existing data center infrastructures without requiring any changes to enterprise specifications, warranty conditions, or form factors.

Storage

TSMC Jumps Into Silicon Photonics, Lays Out Roadmap For 12.8 Tbps COUPE On-Package Interconnect Optical connectivity – and especially silicon photonics – is expected to become a crucial technology to enable connectivity for next-generation datacenters, particularly those designed HPC applications. With ever-increasing bandwidth requirements needed to keep up with (and keep scaling out) system performance, copper signaling alone won't be enough to keep up. To that end, several companies are developing silicon photonics solutions, including fab providers like TSMC, who this week outlined its 3D Optical Engine roadmap as part of its 2024 North American Technology Symposium, laying out its plan to bring up to 12.8 Tbps optical connectivity to TSMC-fabbed processors.

TSMC's Compact Universal Photonic Engine (COUPE) stacks an electronics integrated circuit on photonic integrated circuit (EIC-on-PIC) using the company's SoIC-X packaging technology. The foundry says that usage of its SoIC-X enables the lowest impedance at the die-to-die interface and therefore the highest energy efficiency. The EIC itself is produced at a 65nm-class process technology.

TSMC's 1st Generation 3D Optical Engine (or COUPE) will be integrated into an OSFP pluggable device running at 1.6 Tbps. That's a transfer rate well ahead of current copper Ethernet standards – which top out at 800 Gbps – underscoring the immediate bandwidth advantage of optical interconnects for heavily-networked compute clusters, never mind the expected power savings.

Looking further ahead, the 2nd Generation of COUPE is designed to integrate into CoWoS packaging as co-packaged optics with a switch, allowing optical interconnections to be brought to the motherboard level. This version COUPE will support data transfer rates of up to 6.40 Tbps with reduced latency compared to the first version.

TSMC's third iteration of COUPE – COUPE running on a CoWoS interposer – is projected to improve on things one step further, increasing transfer rates to 12.8 Tbps while bringing optical connectivity even closer to the processor itself. At present, COUPE-on-CoWoS is in the pathfinding stage of development and TSMC does not have a target date set.

Ultimately, unlike many of its industry peers, TSMC has not participated in the silicon photonics market up until now, leaving this to players like GlobalFoundries. But with its 3D Optical Engine Strategy, the company will enter this important market as it looks to make up for lost time.

Related Reading

- TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power

- TSMC 2nm Update: N2 In 2025, N2P Loses Backside Power, and NanoFlex Brings Optimal Cells

- TSMC Preps Cheaper 4nm N4C Process For 2025, Aiming For 8.5% Cost Reduction

- TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips

Semiconductors

Samsung Unveils 10.7Gbps LPDDR5X Memory - The Fastest Yet Samsung today has announced that they have developed an even faster generation of LPDDR5X memory that is set to top out at LPDDR5X-10700 speeds. The updated memory is slated to offer 25% better performance and 30% greater capacity compared to existing mobile DRAM devices from the company. The new chips also appear to be tangibly faster than Micron's LPDDR5X memory and SK hynix's LPDDR5T chips.

Samsung's forthcoming LPDDR5X devices feature a data transfer rate of 10.7 GT/s as well as maximum capacity per stack of 32 GB. This allows Samsung's clients to equip their latest smartphones or laptops with 32 GB of low-power memory using just one DRAM package, which greatly simplifies their designs. Samsung says that 32 GB of memory will be particularly beneficial for on-device AI applications.

Samsung is using its latest-generation 12nm-class DRAM process technology to make its LPDDR5X-10700 devices, which allows the company to achieve the smallest LPDDR device size in the industry, the memory maker said.

In terms of power efficiency, Samsung claims that they have integrated multiple new power-saving features into the new LPDDR5X devices. These include an optimized power variation system that adjusts energy consumption based on workload, and expanded intervals for low-power mode that extend the periods of energy saving. These innovations collectively enhance power efficiency by 25% compared to earlier versions, benefiting mobile platforms by extending battery life, the company said.

“As demand for low-power, high-performance memory increases, LPDDR DRAM is expected to expand its applications from mainly mobile to other areas that traditionally require higher performance and reliability such as PCs, accelerators, servers and automobiles,” said YongCheol Bae, Executive Vice President of Memory Product Planning of the Memory Business at Samsung Electronics. “Samsung will continue to innovate and deliver optimized products for the upcoming on-device AI era through close collaboration with customers.”

Samsung plans to initiate mass production of the 10.7 GT/s LPDDR5X DRAM in the second half of this year. This follows a series of compatibility tests with mobile application processors and device manufacturers to ensure seamless integration into future products.

DRAM

TSMC's 1.6nm Technology Announced for Late 2026: A16 with "Super Power Rail" Backside Power With the arrival of spring comes showers, flowers, and in the technology industry, TSMC's annual technology symposium series. With customers spread all around the world, the Taiwanese pure play foundry has adopted an interesting strategy for updating its customers on its fab plans, holding a series of symposiums from Silicon Valley to Shanghai. Kicking off the series every year – and giving us our first real look at TSMC's updated foundry plans for the coming years – is the Santa Clara stop, where yesterday the company has detailed several new technologies, ranging from more advanced lithography processes to massive, wafer-scale chip packing options.

Today we're publishing several stories based on TSMC's different offerings, starting with TSMC's marquee announcement: their A16 process node. Meanwhile, for the rest of our symposium stories, please be sure to check out the related reading below, and check back for additional stories.

- TSMC 2nm Update: N2 In 2025, N2P Loses Backside Power, and NanoFlex Brings Optimal Cells

- TSMC Preps Cheaper 4nm N4C Process For 2025, Aiming For 8.5% Cost Reduction

- TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips

- TSMC Jumps Into Silicon Photonics, Lays Out Roadmap For 12.8 Tbps COUPE On-Package Interconnect

Headlining its Silicon Valley stop, TSMC announced its first 'angstrom-class' process technology: A16. Following a production schedule shift that has seen backside power delivery network technology (BSPDN) removed from TSMC's N2P node, the new 1.6nm-class production node will now be the first process to introduce BSPDN to TSMC's chipmaking repertoire. With the addition of backside power capabilities and other improvements, TSMC expects A16 to offer significantly improved performance and energy efficiency compared to TSMC's N2P fabrication process. It will be available to TSMC's clients starting H2 2026.

TSMC A16: Combining GAAFET With Backside Power Delivery

At a high level, TSMC's A16 process technology will rely on gate-all-around (GAAFET) nanosheet transistors and will feature a backside power rail, which will both improve power delivery and moderately increase transistor density. Compared to TSMC's N2P fabrication process, A16 is expected to offer a performance improvement of 8% to 10% at the same voltage and complexity, or a 15% to 20% reduction in power consumption at the same frequency and transistor count. TSMC is not listing detailed density parameters this far out, but the company says that chip density will increase by 1.07x to 1.10x – keeping in mind that transistor density heavily depends on the type and libraries of transistors used.

The key innovation of TSMC's A16 node, is its Super Power Rail (SPR) backside power delivery network, a first for TSMC. The contract chipmaker claims that A16's SPR is specifically tailored for high-performance computing products that feature both complex signal routes and dense power circuitry.

As noted earlier, with this week's announcement, A16 has now become the launch vehicle for backside power delivery at TSMC. The company was initially slated to offer BSPDN technology with N2P in 2026, but for reasons that aren't entirely clear, the tech has been punted from N2P and moved to A16. TSMC's official timing for N2P in 2023 was always a bit loose, so it's hard to say if this represents much of a practical delay for BSPDN at TSMC. But at the same time, it's important to underscore that A16 isn't just N2P renamed, but rather it will be a distinct technology from N2P.

TSMC is not the only fab pursuing backside power delivery, and accordingly, we're seeing multiple variations on the technique crop up at different fabs. The... Semiconductors

Qualcomm Intros Snapdragon X Plus, Details Complete Snapdragon X Launch Day Chip Stack As Qualcomm prepares for the mid-year launch of their forthcoming Snapdragon X SoCs for PCs, and the eagerly anticipated Oryon CPU cores within, the company is finally shoring up their official product plans, and releasing some additional technical details in the process. Thus far the company has been demonstrating their Snapdragon X Elite SoC in its highest-performing, fully-enabled configuration. But the retail Snapdragon X Elite will not be a single part; instead, Qualcomm is preparing a whole range of chip configurations for various price/performance tiers in the market. Altogether, there will be 3 Snapdragon X Elite SKUs that differ in CPU and GPU performance.

As well, the company is introducing a second Snapdragon X tier, Snapdragon X Plus, for those SKUs positioned below the Elite performance tier. As of today, this will be a single configuration. But if the Snapdragon X lineup is successful and demand warrants it, I would not be surprised to see Qualcomm expand it further – as they have certainly left themselves the room for it in their product stack. In the meantime, with Qualcomm’s expected launch competition now shipping (Intel Core Ultra Meteor Lake and AMD Ryzen Mobile 8040 Hawk Point), the company is also very confident that even these reduced performance Snapdragon X Plus chips will be able to beat Intel and AMD in multithreaded performance – never mind the top-tier Snapdragon X Elite chips.

Qualcomm will be launching this expanded four chip stack at once; so both Snapdragon X Elite and Snapdragon X Plus tier devices should be available at the same time. The company’s goal is still to have devices on the shelf “mid-year”, although the company isn’t providing any more precise guidance than that. With Qualcomm’s CEO, Cristiano Amon, set to deliver a Computex keynote in June, I expect we’ll get more specific details on timings then, along with the company and its partners using the event to announce and showcase some retail laptop designs. So this is very much looking like a summer launch at the moment.

In the meantime, Qualcomm is already showing off what their Snapdragon X Plus chips can do with a fresh set of live benchmarks, akin to their Snapdragon X Elite performance previews from October 2023. We’ll dive into those in a bit, but suffice it to say, Qualcomm knows the score, and they want to make sure the entire world knows when they’re winning.

CPUs

The Eurocom 780W AC Power Adapter Review: Big Power For Big Laptops While desktop PC power supplies receive the bulk of enthusiasts’ attention for good reasons – not the least of which being the vast selection of options that comes from being a standardized part – power supplies as a whole aren’t just a concern for big PCs. With the majority of PC sales having flipped to notebook sales some years ago, notebook power supplies already lead the market in volume. And while most laptops don’t need the kind of massively powered PSUs that dominate the desktop space, even that is slowly changing as desktop replacement-class laptops increasingly grow in performance and power consumption.

Perhaps the poster-child for the high-performance, high-powered laptop is Eurocom, who has a long history of developing heavy-duty DTR laptops that are all but portable desktop systems. Following recent trends in GPU power consumption and in GPU popularity for both gaming and AI workloads, the company has been selling a range of “mobile supercomputers”, which are practically large, tailor-made laptops that rival even the best of desktop computers – and have the power requirements to match.

In order to power their own high-end laptops, Eurocom has developed a rather unusual 780W AC adapter for high-performance laptops. Intended to power the most powerful of powerful laptops, their latest power adapter can supply over three-quarters of a kilowatt of DC power; a desktop-like wattage for a desktop-like device. It’s a laptop power adapter that’s unique in its scale, and with some room to scale up even further.

| Eurocom 780W AC Adapter Power specifications |

|

| RAIL | +20V |

| MAX OUTPUT | 39A |

| 780W | |

| DIMENSIONS | 325 x 110 x 40mm, 1.38kg |

| AC INPUT | 90 - 264 VAC, 50 - 60 Hz |

| MSRP | PSU: $299, Cable: $129+ |